如何看fpga具体型号 必看TMS320C6678Kintex-7开发板

前 言

本文主要介绍基于Vivado的FPGA案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4。其中案例包括led_flash案例、key_test案例、ibert_eyescan案例、udp_10g_echo案例、fmc_AD9706_ad9613案例、bram_srio_target案例。

本次测试板卡为TMS320C6678+Kintex-7 的FPGA高端异核开发板,它采用TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP以及Xilinx Kintex-7 FPGA处理器设计。

FPGA案例位于产品资料“4-软件资料\Demo\FPGA_Demo\”的FPGA-HDL-demos和FPGA-BlockDesign-demos目录中。案例包含project和bin两个目录,其中project目录下包含案例工程文件,bin目录下含有案例.bit和.bin格式可执行文件。.bit格式文件用于在线加载,.bin格式文件用于固化至SPI FLASH。

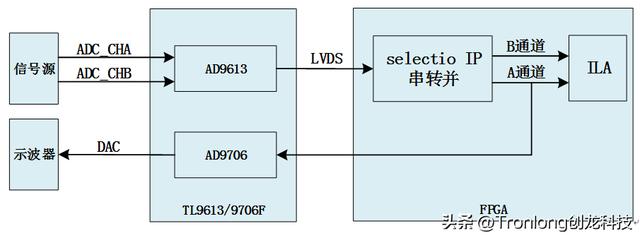

fmc_ad9706_ad9613案例案例功能

案例功能:评估板通过AD9613以175MSPS速率采集AD数据后,再通过ILA显示AD数据波形,再将AD9613的A通道数据通过AD9706以175MSPS刷新率进行DA数据输出,验证高速AD/DA功能。

图 51 程序功能框图

操作说明

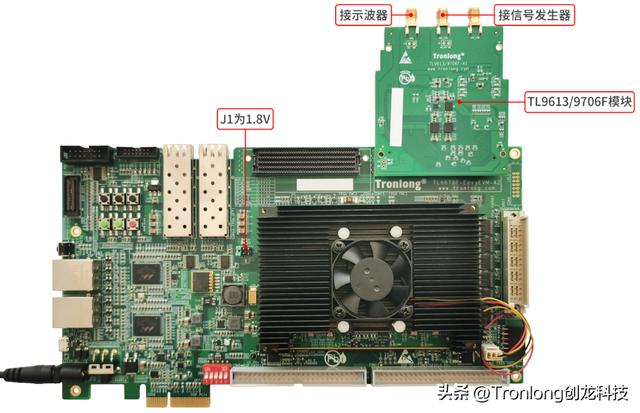

将创龙科技的高速AD/DA模块TL9613/9706F连接至评估板FMC1接口,评估板J1跳线帽选择1.8V档位,以配置FMC IO的BANK电压为1.8V。

使用信号发生器向TL9613/9706F模块的A通道(CON2)提供测试信号,将信号发生器设置为一路正弦波输出,频率设置为1.5MHz,峰峰值设置为1.660Vpp,输出负载设置为50Ω,并使用示波器测试TL9613/9706F模块的DAC接口(CON4)信号。

图 52

图 53

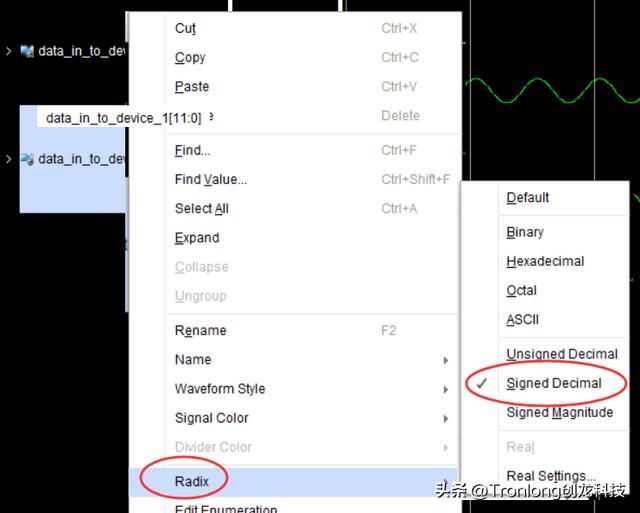

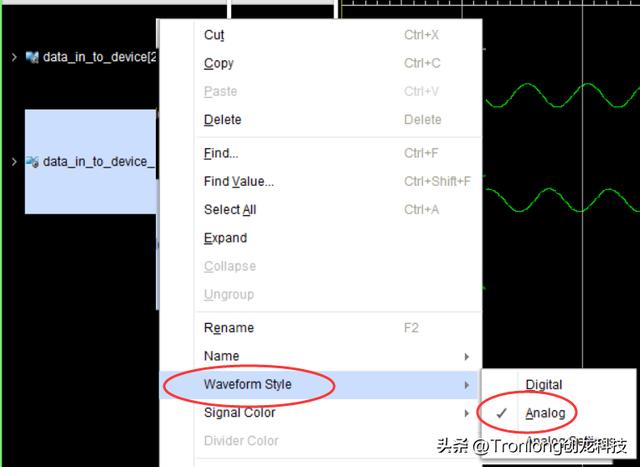

请运行程序,在Vivado工程中分别右击B通道数据data_in_to_device[11:0]和A通道数据data_in_to_device[23:12],点击"Radix -> Signed Decimal"将数据设置为有符号类型,点击"Waveform Style -> Analog"将数据设置为模拟波形。

图 54

图 55

点击

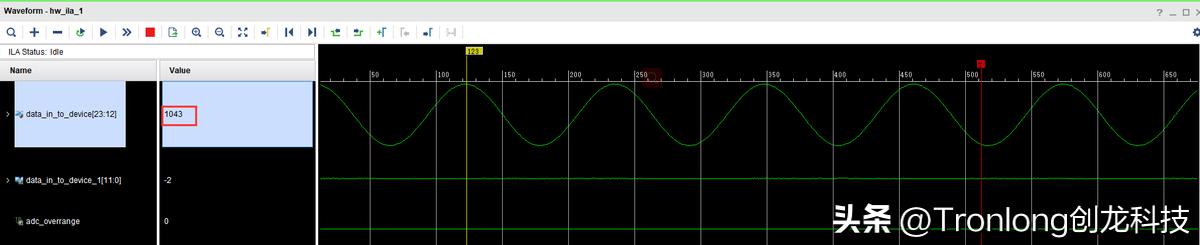

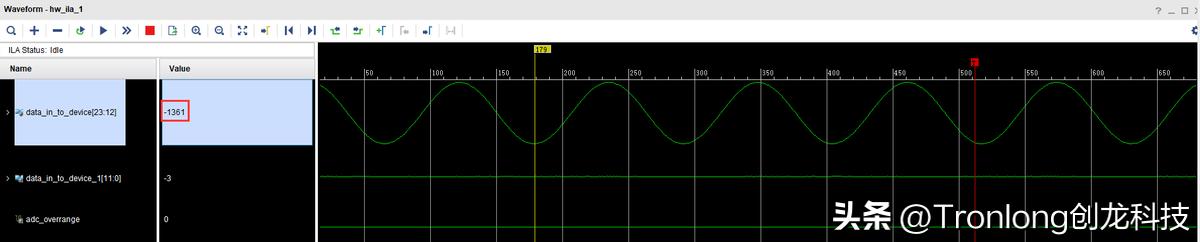

图标,可查看到ILA触发抓取AD数据波形。本次测得波峰值为1043,波谷值为-1361,则峰峰值为1043-(-1361)=2404。

图 56

图 57

AD9613量程为1.75Vpp,TL9613/9706F模块的AD输入增益为0.511。使用示波器通过TL9613/9706F模块的J2测试点,实际测得信号发生器产生的测试信号的峰峰值为2.06Vpp。根据AD9613数据手册,理论幅值=峰峰值*增益/量程*4096=2.06*0.511/1.75*4096=2463.82,与ILA结果基本一致。

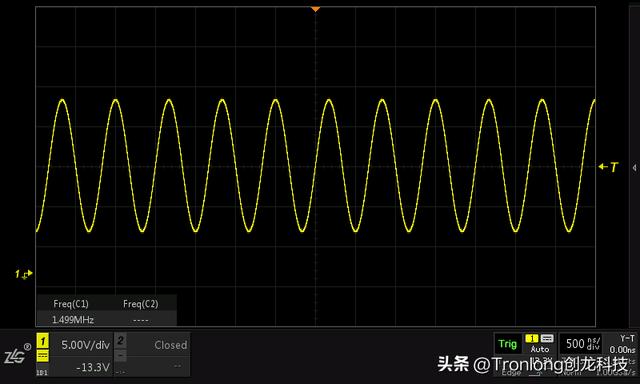

此时,可从示波器中看到DAC接口输出频率为1.499MHz的正弦波,与信号发生器产生的信号基本一致。

图 58

关键代码

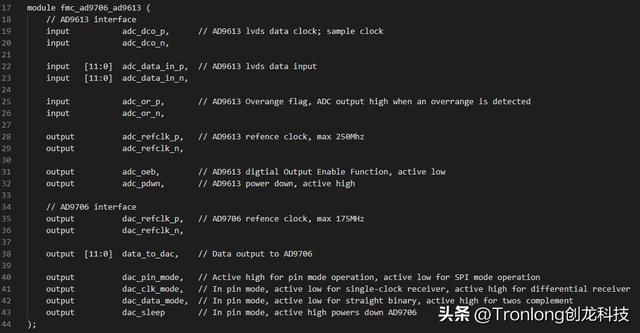

顶层文件为"project\fmc_ad9706_ad9613.srcs\sources_1\imports\hdl\fmc_ad9706_ad9613.v",关键代码说明如下。

端口定义。

图 59

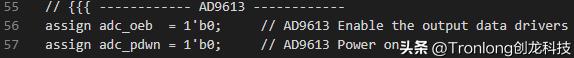

使能AD9613。

图 60

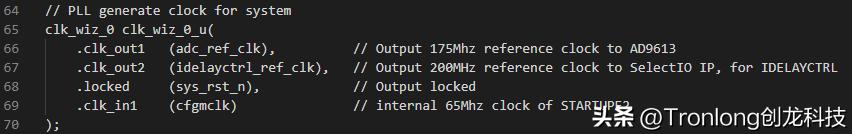

使用原语STARTUPE2输出65MHz系统参考时钟,并用clk_wiz_0 IP核产生各个模块工作时钟。其中ADC_ref_clk为175MHz,用作AD9613参考时钟。idelayctrl_ref_clk为200MHz,用作IDELAYCTRL参考时钟。

图 61

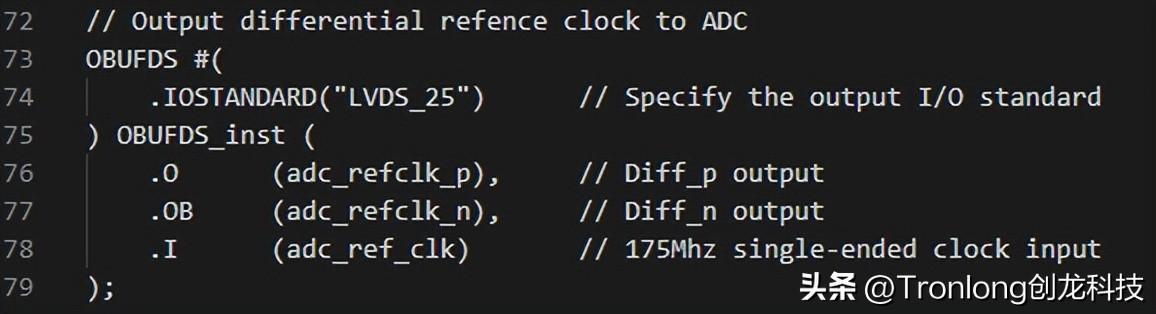

将175MHz单端时钟转换成差分时钟输出至AD9613。

图 62

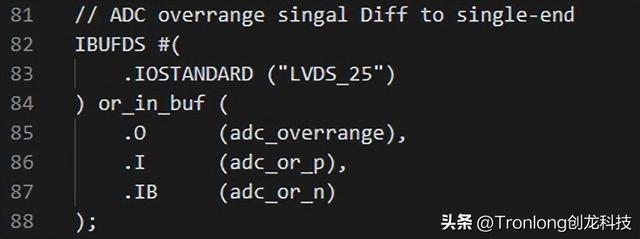

将AD9613的超量程差分信号转换为超量程单端信号。当输入信号幅值超量程时,该信号为高电平;当输入信号幅值未超过量程时,该信号为低电平。

图 63

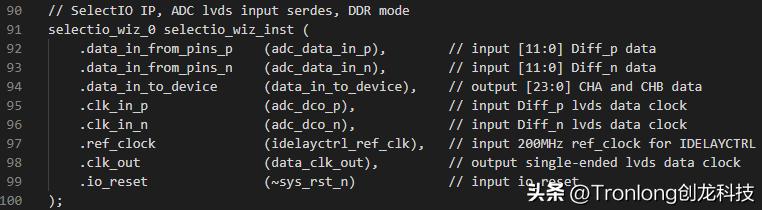

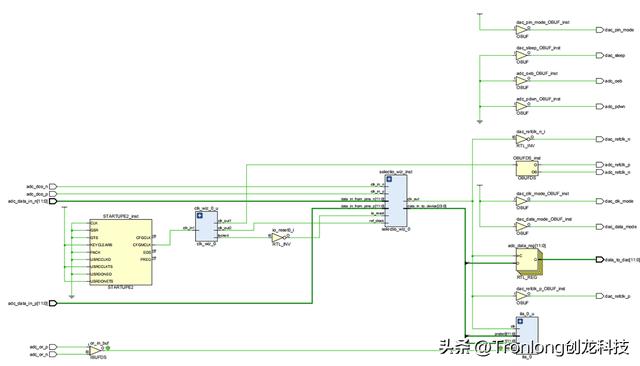

ADC驱动模块。使用SelectIO IP核,将AD9613的差分信号(adc_data_p/n)转换为并行信号(data_in_to_device)。

图 64

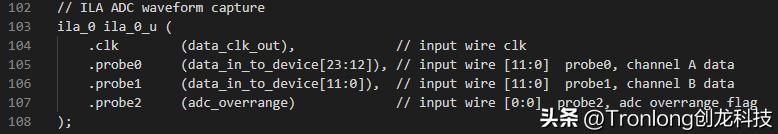

使用ILA抓取AD数据和超量程信号。

图 65

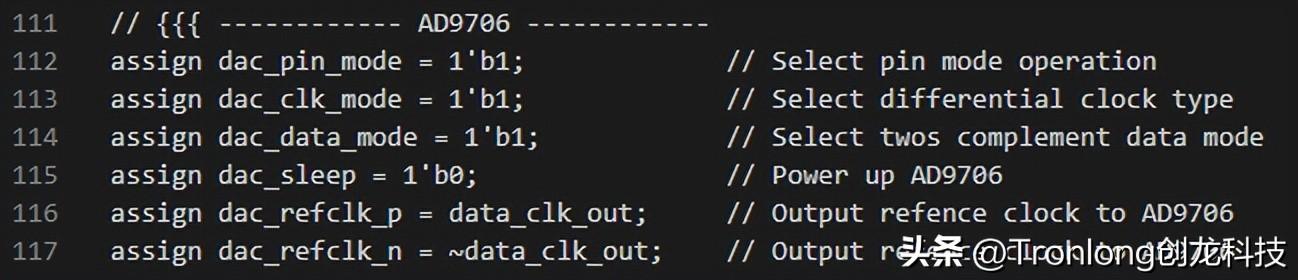

配置AD9706为Pin Mode模式,参考时钟为差分模式,数据格式为二进制补码模式(因AD9613数据格式亦为补码形式),使能AD9706,输出175MHz参考时钟至AD9706。

图 66

将AD9613的A通道数据输出至AD9706。

图 67

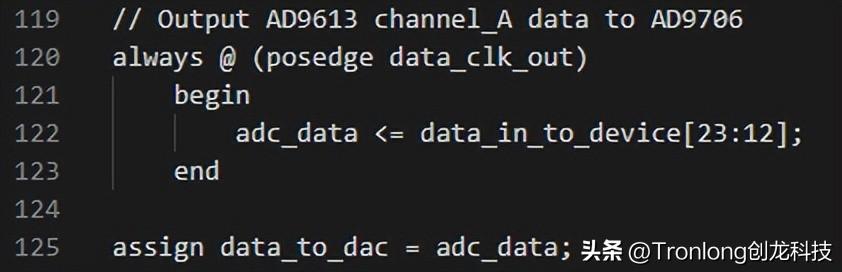

RTL原理图如下图所示:

图 68

IP核配置

本案例使用SelectIO(SelectIO Interface Wizard) IP核将AD9613输出的差分数据转换为并行数据。

SelectIO IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg070-selectio-wiz.pdf》,具体配置说明如下。

配置Data Bus Direction为Input,Data Rate为DDR,数据位宽为12bit,IO类型为差分。

图 69

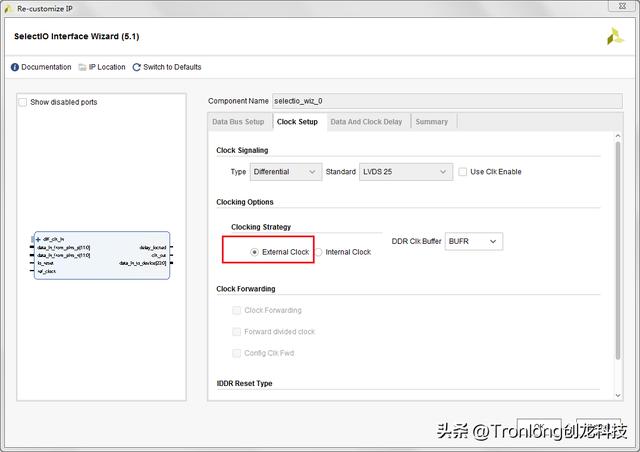

设置该IP核使用AD9613数据传输差分时钟作为参考时钟。

图 70

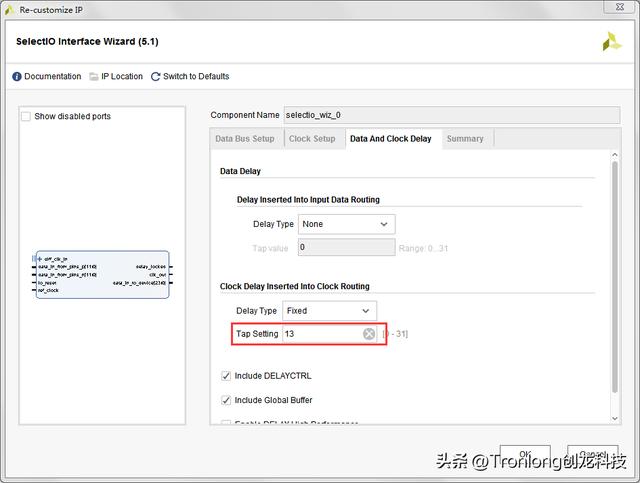

Tap Setting设置为13,将数据传输时钟的边沿与数据的边沿错开,以提高数据采集的准确性,不同板卡可能需设置为不同的值,以实际测试结果为准。IDELAYCTRL参考时钟ref_clock=200MHz,则ref_clock_period=1/200MHz=0.5ns=5000ps。Tap setting的取值范围为0~31,共32个Tap,则一个Tap=ref_clock_period/2/32=78ps。将数据传输时钟的边沿移动13个Tap(78ps*13=1014ps),避免数据和时钟同时发生跳变而导致数据出错。

图 71

bram_srio_target案例案例功能

案例功能:评估板DSP端和FPGA端进行SRIO通信测试,并统计读写速率。评估板DSP端作为Initiator,评估板FPGA端作为Target。SRIO默认配置为x4模式,每个通道速率5Gbps,并分别使用NWRITE NREAD和SWRITE NREAD模式进行测试。FPGA端使用一个36Kbit的BRAM作为设备存储空间,将DSP端发送的过来数据储存至BRAM。

本案例的DSP端测试程序为“4-软件资料\Demo\DSP_Demo\noOS-demos\srio_initiator\”。为便于查找,我司在本案例的bin目录下提供了DSP端测试程序可执行文件srio_initiator_noOS.out。

操作说明

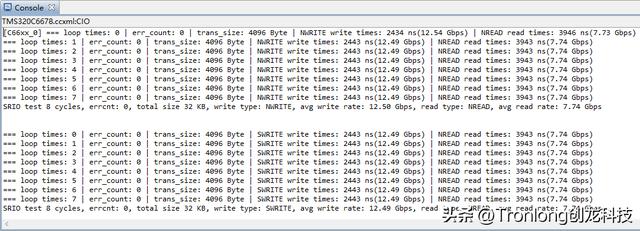

请先运行FPGA端程序,再运行DSP端程序,DSP端的CCS Console窗口将打印测试结果。

NWRITE NREAD模式:NWRITE=12.50Gbps NREAD=7.74Gbps

SWRITE NREAD模式:SWRITE=12.49Gbps NREAD=7.74Gbps

备注:由于写测试仅统计发送数据至SRIO FIFO的时间,读测试统计发送读请求并等待Target发送数据完成的时间,因此写速率将比读速率高。

图 72

关键代码

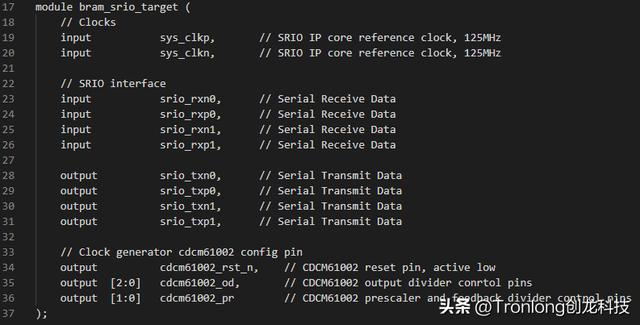

顶层文件为"project\bram_srio_target.srcs\sources_1\imports\hdl\bram_srio_target.v",关键代码说明如下。

端口定义。

图 73

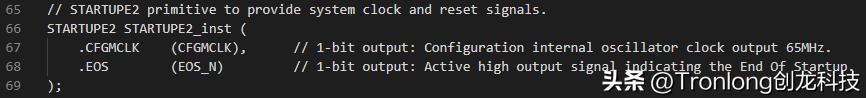

使用STARTUPE2原语提供的EOS作为系统复位信号,CFGMCLK(65MHz)作为系统时钟。

图 74

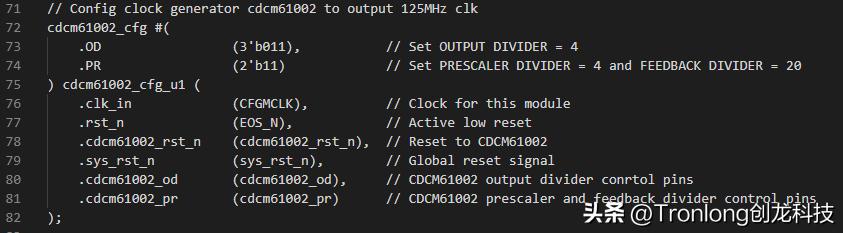

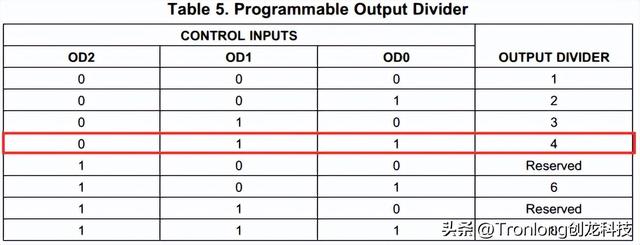

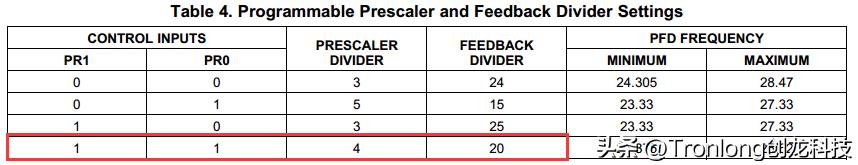

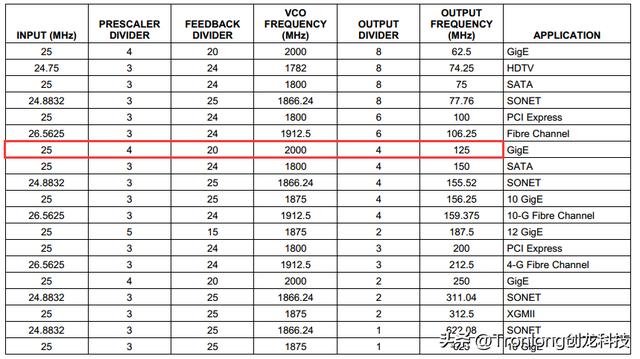

将时钟芯片CDCM61002的OD[2:0]管脚电平配置成011,PR[1:0]管脚电平配置成11,向Serial RapidIO Gen2 IP核提供125MHz的参考时钟。

图 75

图 76

图 77

图 78

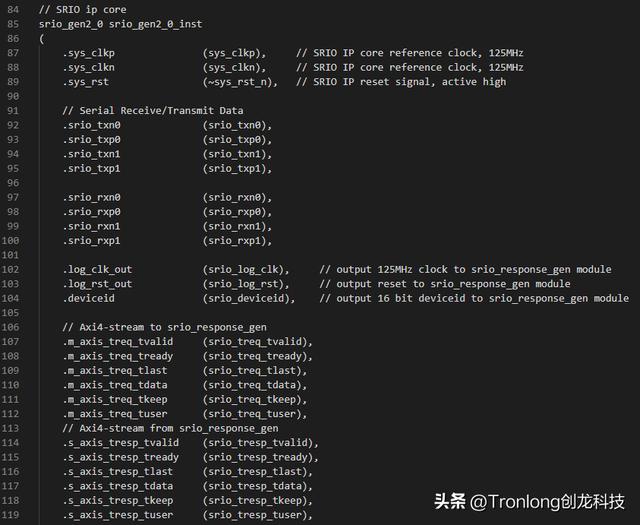

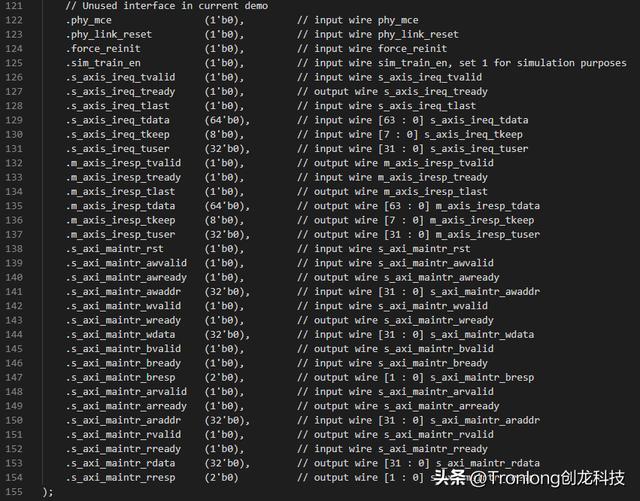

例化Serial RapidIO Gen2 IP核。

图 79

图 80

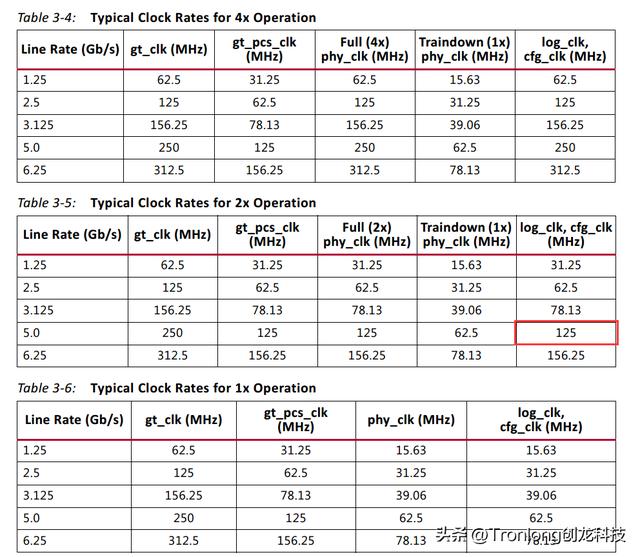

其中Serial RapidIO Gen2 IP核输出的log_clk为125MHz。

图 81

调用srio_response_gen模块,其接口与Serial RapidIO Gen2 IP核连接。

图 82

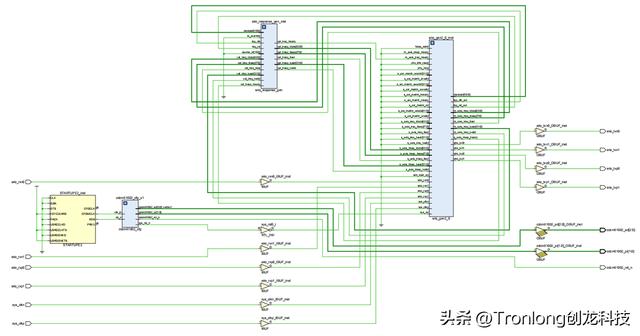

RTL原理图如下所示:

图 83

模块/IP核配置cdcm61002_cfg模块

本案例使用cdcm61002_cfg模块配置CDCM61002输出125MHz时钟,作为Serial RapidIO Gen2 IP核的参考时钟。

时钟芯片具体配置方式请查阅“6-开发参考资料\数据手册\核心板元器件\CLOCK\”目录下的《cdcm61002.pdf》。cdcm61002_cfg模块源码为"project\bram_srio_target.srcs\sources_1\imports\hdl\cdcm61002_cfg.v"。

Serial RapidIO Gen2 IP核

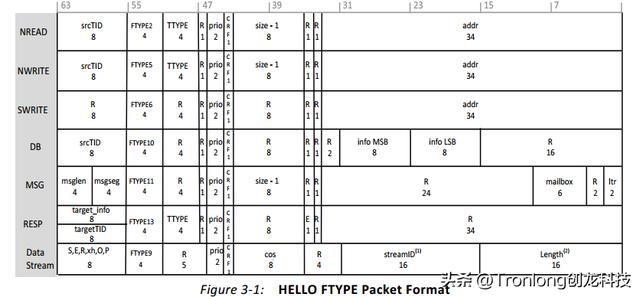

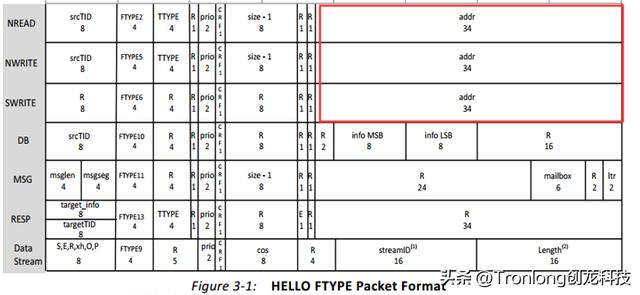

本案例使用Serial RapidIO Gen2 IP核实现FPGA与DSP通过SRIO接口进行通信,使用HELLO(Header Encoded Logical Layer Optimized)格式,支持NREAD、NWRITE、NWRITE_R、NWRITE_R、DOORBELL、MESSG等Response Packet操作。

Serial RapidIO Gen2 IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg007_srio_gen2.pdf》,具体配置说明如下。

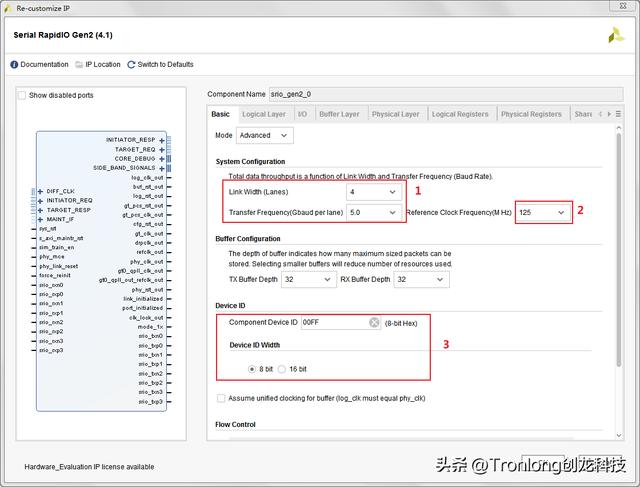

设置SRIO链路宽度为4 Lanes,每个Lane传输频率为5Gbps,参考时钟为125MHz,8bit位宽ID=0XFF。

图 84

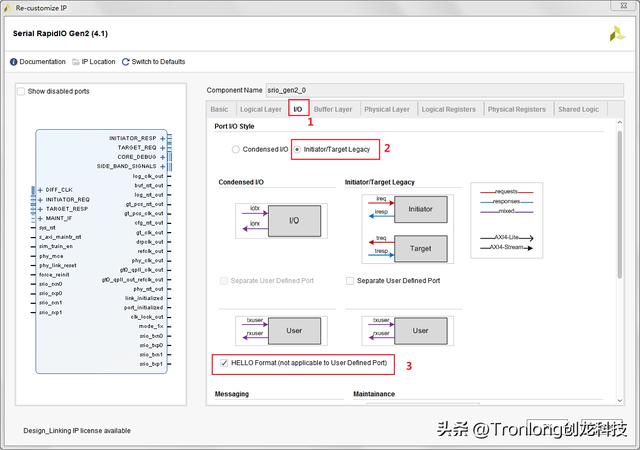

点击I/O,Port I/O Style选择为Initiator/Target Legacy模式,其中Condensed I/O接收和发送均使用一个AXI4-Stream通道,Initiator/Target Legacy接收和发送采用不同的AXI4-Stream通道,I/O端口配置使用HELLO格式包,其他参数保持默认值即可。

图 85

srio_response_gen模块

本案例使用srio_response_gen模块为接收到的请求事务生成对应的响应事务。

srio_response_gen模块开发说明为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg007_srio_gen2.pdf》的Detailed Example Design章节。srio_response_gen模块源码为"project\bram_srio_target.srcs\sources_1\imports\hdl\srio_response_gen.v",关键代码说明如下。

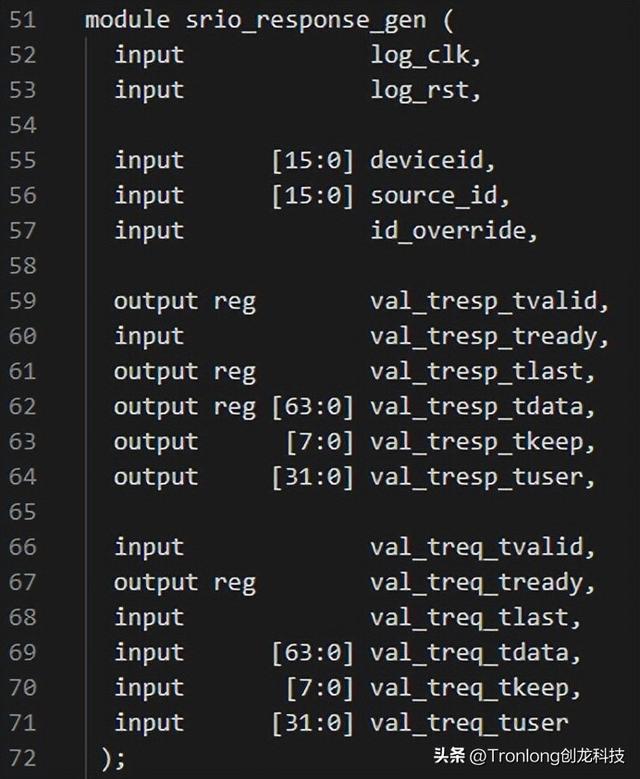

log_clk和log_rst分别为逻辑层时钟与复位。tresp和treq分别为两个AXI4-Stream通道,tresp是响应事务传输通道,treq是请求事务传输通道。deviceid为Initiator发送过来的数据包中包含的Device ID,Source_id和id_override未使用,默认均为0。

图 86

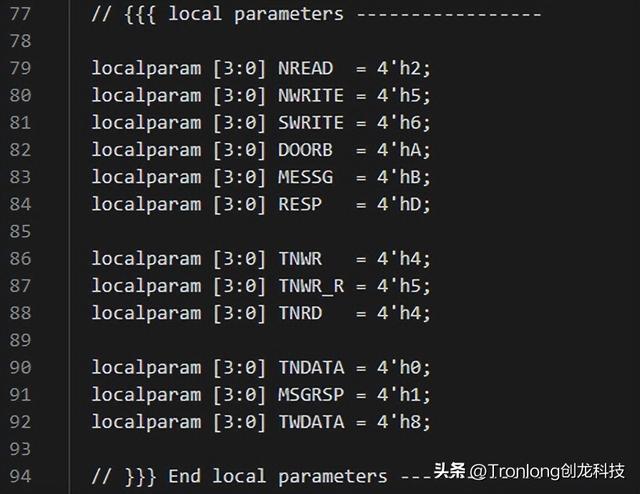

定义HELLO格式包头中的FTYPE字段与TTYPE字段的值,此两个字段的值与事务类型有关。

图 87

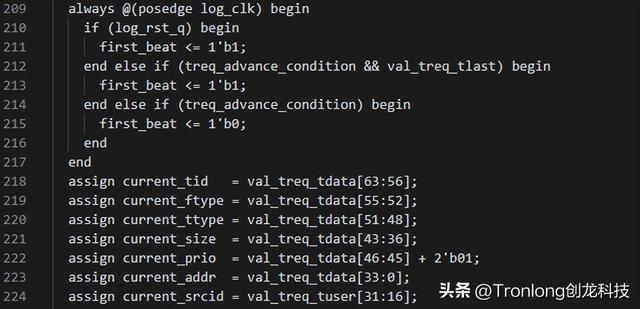

将Initiator发过来的请求treq_tdata中的数据,按照HELLO格式的定义把对应的关键字段分离出来。

图 88

图 89

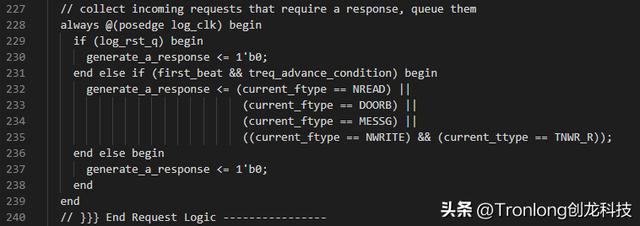

生成有响应事务的标志。

图 90

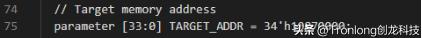

配置Initiator发送过来的读写事务的基地址为0x10870000,如Initiator发送的读写事务的目标地址的第31位至16位为0x1087,则数据将会从实际地址读出。如Initiator发送的读写事务的目标地址的第31位至16位非0x1087,则数据包的数据将被丢弃。

图 91

图 92

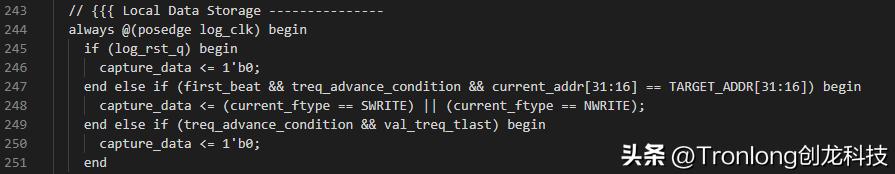

当地址字段的第31位至第16位为0x1087时,写事务的数据方可被存放至BRAM。

图 93

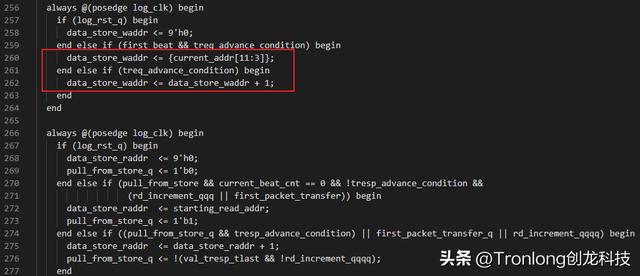

产生数据存储的写地址信号data_store_waddr和读地址信号data_store_raddr。由于srio_response_gen模块的数据位宽为64bit,即一次从BRAM读或写8Bytes数据,同时一个地址对应一个字节,则每读写8Bytes数据地址需要递增8位,因此地址位从current_addr[11:3]开始并递增。

图 94

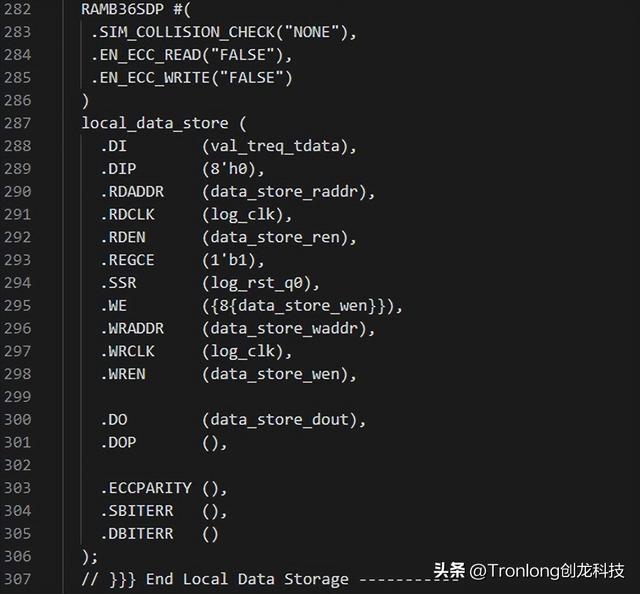

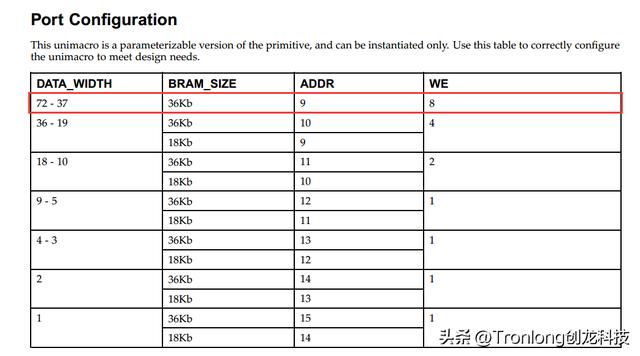

例化一个RAMB36SDP来存储数据。DATA_WIDTH为64bit,ADDR为9bit,即总容量为2^9 x (64/8) = 4KByte。

图 95

图 96

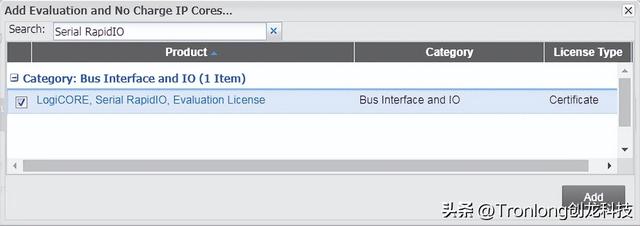

申请IP核License

如需重新编译工程或打开Serial RapidIO Gen2 IP核,需在Xilinx官网申请Serial RapidIO Gen2 IP核的免费License,并将其正确导入。License申请与导入方法,请查阅开发环境搭建文档相关章节,其他IP核无需License。

图 97

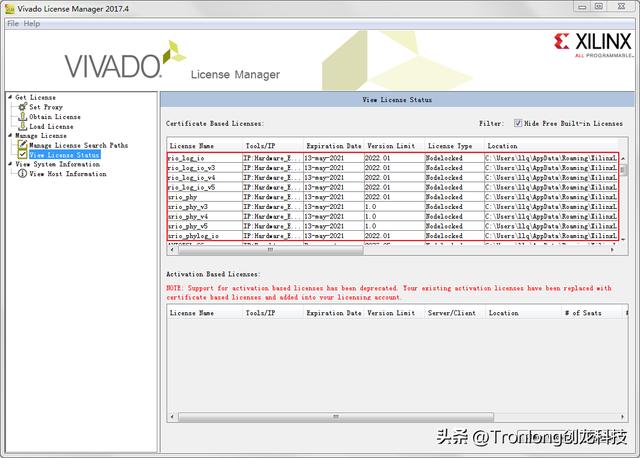

成功导入License后,点击"View License Status"可以查看新添加的IP核License。

图 98

由于篇幅问题,文章分为上下两篇,本文为下篇,感兴趣的可以查阅观看,谢谢支持!

,